# SOI-MEMS Foundry Services at CeNSE

# One step solution for MEMS Manufacturing

MPW | CeNSE | Sudhanshu Shekhar

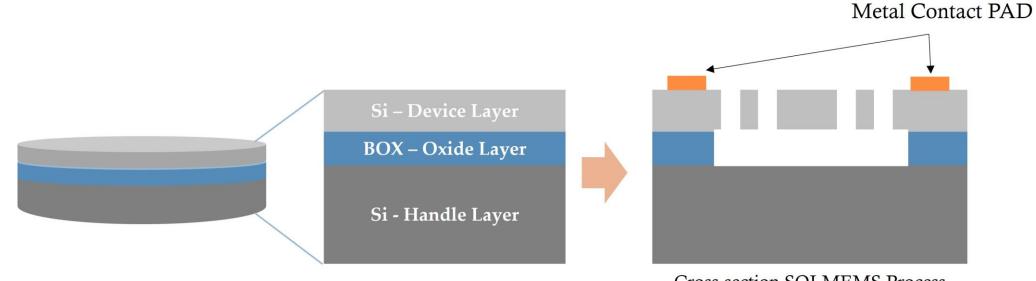

#### Silicon-On-Insulator (SOI) Wafer

Cross-section SOI-MEMS Process

Layer features:

Device layer : 20 µm

Buried Oxide :  $1 - 2 \mu m$

#### Handle layer : 500 µm

- Layer feature:

- Device layer thickness (SOI): 20  $\mu m$

- Handle layer thickness (Si): 500 µm

- Buried oxide (BOX):  $1 2 \mu m$

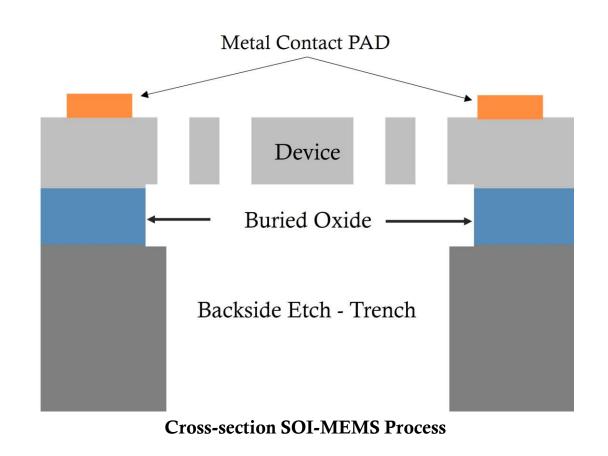

- **<u>Device layer</u>** is used to fabricate mechanical structures such as cantilever, resonators, resistors

- **<u>Buried oxide (BOX)</u>** acts as a sacrificial layer which is removed using HF to release the structure

- <u>Contact PAD</u> Au/Cr (20/200 nm) deposited on top of device layer to make electrical connections

- <u>Handle layer</u> or substrate is used to provide mechanical strength

#### Process Flow:

D ENGINEERING

# **Design Rules (1)**

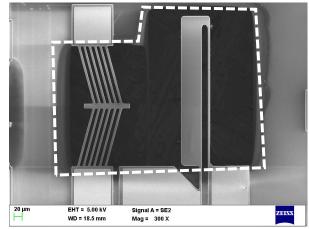

- SOI-MEMS is a 3-mask process.

- Device layer is of single-crystal-silicon (SCS) with a thickness of 20  $\mu$ m.

- The resistivity of device layer is in the range of 1 30 Ohm cm ( $\Omega$ -cm).

| Layer             | Material | Thickness                       | Remark                                         |

|-------------------|----------|---------------------------------|------------------------------------------------|

| L0 – Metal PAD    | Cr/Au    | 20/200 nm                       | Electrical contact - Bond-pad                  |

| L1 – SOI          | Si       | $20 \ \mu m \pm 0.5 \ \mu m$    | Mechanical structures - Beams, Resonators etc. |

| L2 – BOX          | Oxide    | $1 - 2 \ \mu m \pm 0.1 \ \mu m$ | Sacrificial layer                              |

| L3 – Handle wafer | Si       | 500 $\mu$ m $\pm$ 10 $\mu$ m    | Mechanical support                             |

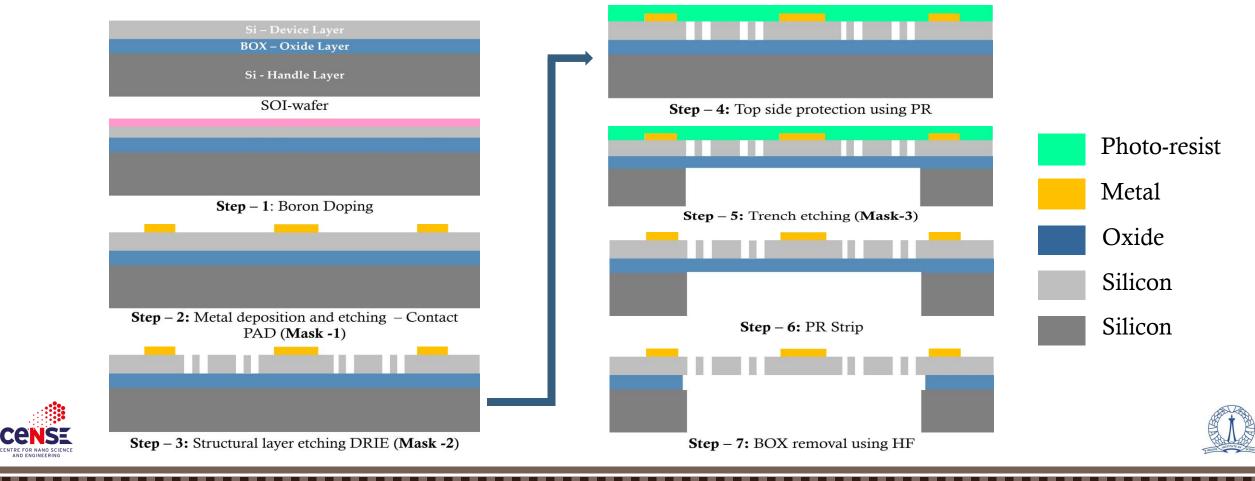

# **Design Rules (2)**

- Key points to remember before staring any design -

- Critical dimension (CD) and Mnemonics associated with each layer

| Mnemonics | Layer Name | <b>Min. Feature (</b> µm) | Min. Space (µm) |

|-----------|------------|---------------------------|-----------------|

| MetalPAD  | CPAD       | 5                         | 5               |

| SOI       | SOI        | 3                         | 5               |

| SOIHOLE   | HOLE       | 10                        | 5               |

| TRENCH    | TRNCH      | 200                       | 100             |

# **Design Rules (3)**

- Key points to remember before staring any design -

- Overlay between two layers

| Layer           | Center-to-Center (µm) | Edge-to-Edge (µm) |

|-----------------|-----------------------|-------------------|

| MetalPAD to SOI | ±5                    | ±5                |

| TRENCH to SOI   | ±5                    | ± 50              |

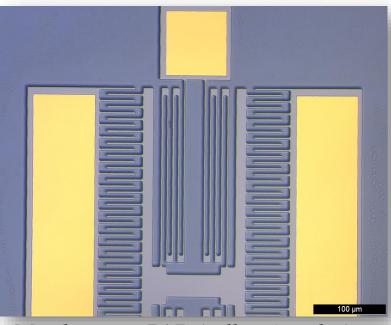

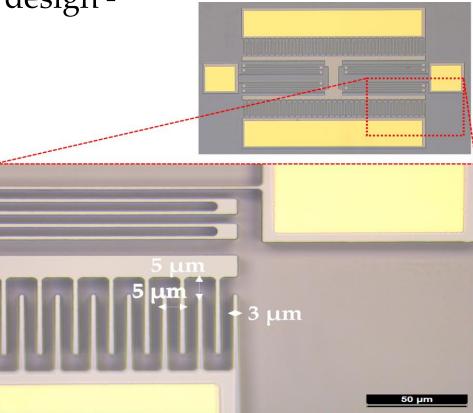

Metal contact PAD (yellow in color) on top of device layer for electrical contact

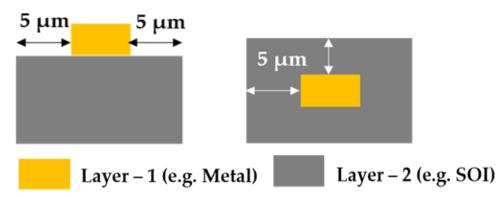

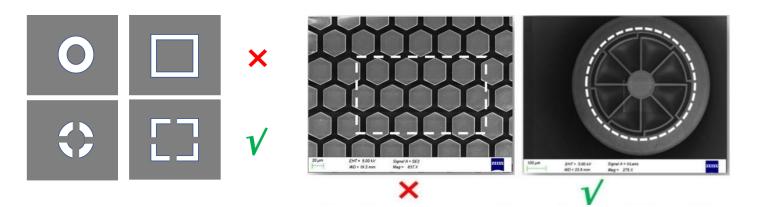

# **Design Rules (4)**

- Key points to remember before staring any design -

- Recommended design format CIF or GDS

- Critical Dimension (CD)

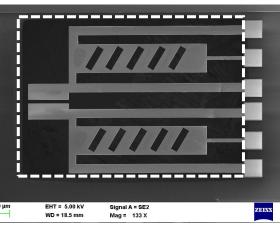

- Min. feature size of microstructures 3 μm

- Minimum spacing between two adjacent microstructures (gap between two comb fingers in case of an electrostatic combdrive actuator) should not be less than 5 µm (see adjacent figures for reference)

# **Design Rules (5)**

- Key points to remember before staring any design -

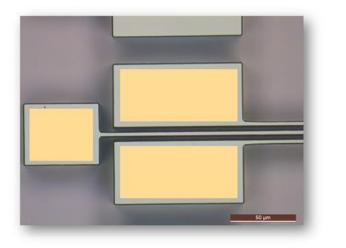

- Contact PAD recommended dimension (see figures for reference)

- On-wafer probe 200 μm × 200 μm

- Bond-pad 500  $\mu$ m × 500  $\mu$ m (wire-bonding)

Metal contact PAD (yellow) on top of device layer for electrical contact

# **Design Rules (6)**

- Key points to remember before staring any design -

- TRENCH -

- No un-anchored structure under the TRENCH

- Minimum feature size 100  $\mu$ m × 100  $\mu$ m

- Center-to-Center  $\leq$  50 µm (Top-to-Bottom Alignment)

# **Design Rules (7)**

- Design layout can be created using any layout editor such as L-edit, K-layout, Clewin, Mentor Graphics and others

- Accepted design formats are CIF and GDS-II

- Users must convert their final designs for the fabrication should be either CIF or GDS-II

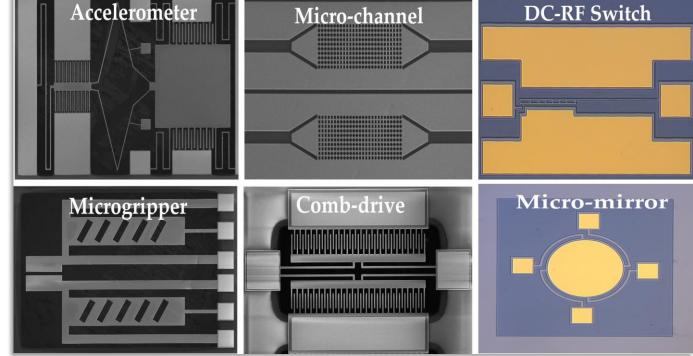

#### What all you can fabricate?

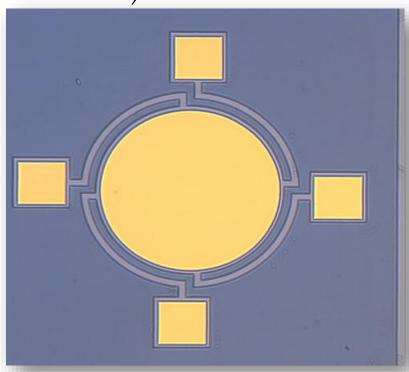

#### **MEMS devices :-**

- Inertial Sensors

- Gyroscope

- Accelerometer

- DC-RF Switches

- Thermal Actuator

- Resonator, Oscillator

- Optical Switches, Waveguides

- Microfluidic Channels

Some of the MEMS devices fabricated using SOI-MEMS Process